# Bias Temperature Instability on SiC n- and p-MOSFETs for High Temperature CMOS Applications

Emran K Ashik<sup>1</sup>, Sundar B Isukapati<sup>2</sup>, Hua Zhang<sup>3</sup>, Tianshi Liu<sup>3</sup>, Utsav Gupta<sup>3</sup>, Adam J Morgan<sup>2</sup>, Veena Misra<sup>1</sup>, Woongje Sung<sup>2</sup>, Ayman Fayed<sup>3</sup>, Anant K. Agarwal<sup>3</sup>, and Bongmook Lee<sup>1</sup>

1. Department of Electrical and Computer Engineering North Carolina State University

Raleigh, NC, USA

Phone: +1 (919) 917-1839, <u>ekashik@ncsu.edu</u>

2. College of Nanoscale Science & Engineering

State University of New York Polytechnic Institute

Albany, NY USA

3. Department of Electrical and Computer Engineering Ohio State University

Columbus, OH, USA

Abstract—The circuit functionalities of Complementary Metal-Oxide-Semiconductor (CMOS) devices on 4H-SiC for digital and analog circuit applications beyond 200°C have been extensively studied, however, the reliability of the devices on SiC needs to be demonstrated due to the traps at/near the dielectric interface. In this report, the reliability of n- and p- Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) has been studied on three different gate oxide conditions - thick thermally grown, ultrathin thermal + thick CVD oxide and ultrathin thermal + thin CVD oxide in terms of their bias temperature instability (BTI) measurement. The MOSFETs were stressed at various constant bias voltages at 150°C and up to 105s. The threshold voltage shift due to positive bias on n-MOSFET is <0.5V after 105s at +25Vwhile p-MOSFET shows a larger shift of -1.9V shift after 105s at -25V and 150°C for ultrathin + thick CVD oxide. The report also establishes improvement in reliability of p-MOSFETs with ultrathin + CVD oxides over thermally grown oxides.

Index Terms—CMOS, reliability, field-effect mobility, threshold voltage, transconductance

## I. INTRODUCTION

SiC has been well-established as a replacement of silicon at harsh conditions such as high field and high temperature due to its superior thermal, mechanical and electrical properties compared to silicon at those conditions [1], [2]. The ability to operate at cryogenic as well as elevated temperatures enables sensing applications such as temperature sensor, gas sensors, pressure sensors and other microelectromechanical systems (MEMS) at extreme environment [3]. As a wide bandgap semiconductor, SiC has the potential for high-power electronics due to high breakdown voltage, low on-resistance, high thermal

The work was funded by Advanced Research Projects Agency-Energy (ARPA-E) U.S. Department of energy, under Award Number DE-AR0001028

conductivity and high radiation tolerance [4]. Both 4H and 6H polytypes have been widely used in high voltage DC-DC converters, aerospace industries, chargers for electronic vehicles and smart high-power home and industry appliances. Digital and analog circuits based on SiC CMOS can operate beyond 200°C [5] where silicon devices have limited operations. Complex integrated circuit (IC) control electronics on SiC such as flipflops (FF), ring oscillators and operational amplifiers (Op Amp) have been demonstrated already at high temperature [5]–[7]. The ability to integrate lateral high voltage (HV) MOSFETs into ICs enables high voltage switching and controlling equipment at extreme conditions [8].

However, one of the major drawbacks of SiC MOSFETs is the density of traps (D<sub>it</sub>) at/near the SiO<sub>2</sub>/SiC interface[9], [10]. Even though thermal oxide can easily be grown on SiC unlike any other wide bandgap semiconductors, a strong increase of D<sub>it</sub> close to the conduction band is observed due to the defects located at the oxide near the SiO<sub>2</sub>/SiC interface. As the silicon carbide crystal is oxidized, carbon-based oxides form complex structures that do not diffuse out of the SiO<sub>2</sub> layer. To passivate the traps near the conduction band, nitridation via NO or N<sub>2</sub>O has been common to SiC MOSFETs [11]–[13]. Recently, incorporation of high-K dielectrics and other deposited oxides has been proven to reduce the interface states and improve mobility [14]–[18].

Even though deposited oxides improve the device characteristics, their low conduction band offsets and poor band alignment with SiC substrate results in higher rate of injection [19]. Higher carrier-injection means capture of electrons/holes through traps and/or generation of traps. The issue becomes severe at elevated temperature since the trapping/de-trapping barrier lowers and raises reliability concerns e.g. threshold voltage shift [20], [21] and time dependent dielectric breakdown [22], [23]. The improvements in reliability and mitigations of instabilities have drawn significant interests lately. A. J. Lelis et al. [24] has reported on an in-depth

understanding of threshold voltage instabilities. The transfer characteristics shift right and left with positive and negative bias stress even after 3 minutes of stress. R. Green et al. [25] observed threshold voltage instability in commerciallyavailable power MOSFETs. A positive shift results in an increase in specific on-resistance while a negative shift increases the leakage current. The polarity of the bias also has an asymmetric effect. With positive bias stress, the threshold voltage of SiC n-MOSFETs exhibited small shifts whereas at negative bias stress, the n-MOSFETs exhibited much larger shifts [26], [27]. Passivation engineering of traps improves the interface states near the conduction band but does not sufficiently passivate traps near the valence band. As a result, there are improvements in the n-MOSFET reliability, where electron is the majority carrier, however the p-MOSFET reliability is still poor and needs to be addressed for potential high temperature CMOS applications. This work reports on performance and reliability studies of both n- and p-channel SiC MOSFETs with ultrathin thermal oxide followed by chemical vapor deposition (CVD) oxide. The results are compared to the standard thermally grown gate oxide.

### II. DESIGN AND FABRICATION PROCESS

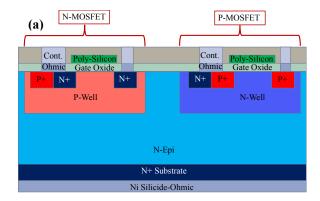

N- and P-channel lateral MOSFETs were fabricated on a 6inch N-epi 4H-SiC Wafer at the Analog Devices Inc. (ADI) Hillview Fabrication facility. The implanted channel MOSFETs were fabricated using aluminium as p-species and nitrogen as n-species. The P-well doping was  $2x10^{16}$  /cm<sup>3</sup> and the N-well doping was  $4 \times 10^{16}$  /cm<sup>3</sup>. The source/drain junctions had  $0.5 \times 10^{19}$  /cm<sup>3</sup> doping concentration of the corresponding species. In this study, three separate gate oxide conditions are reported. Wafer 1 has thermally grown oxide with a target thickness of 50nm. Wafer 2 and Wafer 3 have ultrathin oxide formed by thermal oxidation followed by high-temperature chemical vapor deposition (CVD) oxides with a target thickness of 50 nm (Wafer 2) or 25 nm (Wafer 3). The grown or deposited oxides were annealed at 1250°C in diluted N<sub>2</sub>O for densification and nitridation of the interface. Wafer 3 has shorter duration of post deposition anneal (PDA) due to smaller thickness compared to thicker gate oxides (Wafer 1 and Wafer 2). The thermal oxide was subjected to a separate post oxidation anneal (POA) to better eliminate oxidation clusters due to carbon atoms prior to N<sub>2</sub>O anneal. The gate oxide conditions, and their effective oxide thicknesses (EOTs) extracted from capacitancevoltage characteristics are listed in Table 1. A 0.5µm thick ntype polysilicon layer was deposited and patterned as the gate electrode contact for n- and p-MOSFETs. Ohmic contacts for the junctions were formed using 100 nm Nickel which was annealed at 750°C for two minutes for silicide formation followed by another anneal at 965°C for two minutes to improve the contact. A 1 µm thick interlayer dielectric was deposited, and a 500 nm thick aluminum was used as metal interconnect and contact pads. The cross section of the MOSFETs and a photo of the fabricated 6-inch Wafer (#1) are shown in Fig. 1. A detailed fabrication process can be found in [8].

Figure 1. (a) The cross-sectional view of n- and p-MOSFET. Ni-Silicide was used as ohmic contact and 0.5µm aluminum was used as top metal interconnect. (b) A photo of 6" Wafer with HV and LV nand p-MOSFETs, capacitors, logic IC and test structures.

Table 1. Gate oxide split plan for the three Wafers. EOT is the effective oxide thickness calculated from the capacitancevoltage characteristics.

| Wafer<br>ID | Thermal Oxidation | Ultra-thin<br>Ox | HTO<br>GOx | POA-1       | POA-2                                                         | ЕОТ        |

|-------------|-------------------|------------------|------------|-------------|---------------------------------------------------------------|------------|

| W1          | 40nm at<br>1175°C | N                | N          | 800°C<br>3h | 1250°C diluted N <sub>2</sub> O,<br>20% N <sub>2</sub> , 3h   | 54 nm      |

| W2          | N                 | 2nm              | 40nm       | N           | 1250°C diluted N <sub>2</sub> O,<br>20% N <sub>2</sub> , 3h   | 46.7<br>nm |

| W3          | N                 | 2nm              | 20nm       | N           | 1250°C diluted N <sub>2</sub> O,<br>20% N <sub>2</sub> , 1.5h | 28.9<br>nm |

#### III. CHARACTERIZATION METHODOLOGY

The Capacitance-Voltage (C–V) and current-voltage (I–V) measurement was done using HP 4284 LCR meter and a Keithley 4200SCS system, respectively. EOT was calculated using the formula EOT=  $\epsilon_{ox}*A/C_{OX}$ , where  $C_{OX}$  is the oxide capacitance, A is the capacitor area and  $\epsilon_{ox}$  is the electrical permittivity of SiO<sub>2</sub>. Device parameters including EOT, flatband voltage, surface doping, and bulk potential were extracted using NCSU CVC program [28]. To extract the transfer characteristics, drain was biased at 0.1V and the source

and the substrate is at zero volt. Gate voltage was varied from zero to  $\pm 20$ V. All the devices have W/L = 1 (where, W = channel width, L = channel length) to accurately extract the mobility by minimizing a geometry effect. The field effect mobility was extracted using the following formula,

$$\mu_{FE,peak} = \frac{\max\left(\frac{\delta I_D}{\delta V_{GS}}\right)}{V_{DS}C'_{OX}}$$

Where,  $I_D$  is the drain current,  $V_{GS}$  is gate to source voltage,  $V_{DS}$  is drain to source voltage which is 0.1V throughout this work and  $C'_{OX}$  is the oxide capacitance per unit area (F/cm<sup>2</sup>).

The device reliability is evaluated through bias temperature instability (BTI) measurement. To report BTI measurements, we adopted stress-sense-stress technique [25]. The threshold voltage was primarily extracted using the intercept of maximum slope via linear extrapolation from the transfer characteristics [29] at measurement temperature prior to applying any stress. At this threshold voltage, the current level was determined and used to extract threshold voltage using the current level method [30]. Each BTI measurement was conducted by selecting the current level using this method and extracting only the required portion of transfer characteristics near the selected current level to minimize the delay between two 'stress' steps.

A constant voltage stress was applied to the gate during the "stress" step. The electric field was extracted using the formula,  $E=(V_{BIAS}\text{-}V_{TH})/t_{OX}$  instead of  $E=V_{BIAS}/t_{OX}$  due to the fact that the applied voltage at the gate terminal is not essentially across the gate oxide. Rather, one part is used to provide the surface potential until the flatband of the metal oxide semiconductor (MOS) structure and the other part is across the dielectric [31]. The accurate gate oxide capacitance  $(C_{OX})$  was extracted from capacitance-voltage characteristics of 100 x 100  $\mu m$  MOS capacitor fabricated on N-epi layer. The transfer characteristics, leakage currents, PBTI and NBTI measurements were conducted on 30 x 30  $\mu m$  (W/L = 1) n- and p-channel MOSFETs.

## IV. RESULTS AND DISCUSSIONS

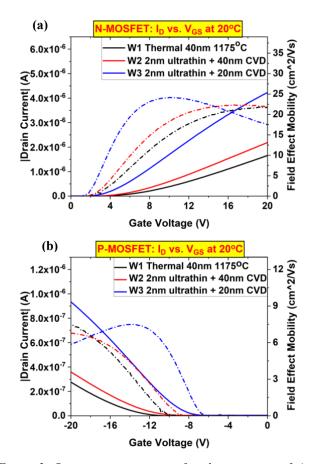

Fig. 2 shows the transfer characteristics of n- and p-MOSFETs at room temperature. The peak field effect mobility for n-MOSFET was 21.8, 22.4 and 24.1 cm<sup>2</sup>/Vs for Wafer 1, 2 and 3 respectively. On the other hand, for p-MOSFET, the mobility values are 7.5, 6.8 and 7.5 cm<sup>2</sup>/Vs for Wafer 1, 2 and 3 respectively. The mobility is higher for ultrathin + CVD oxides compared to thermally grown oxide due to better interface states of ultrathin + CVD oxides. In addition, Wafer 3 has higher mobility than Wafer 2 possibly owing to shorter N<sub>2</sub>O annealing which leads to less interfacial oxidation and C-related traps [9]. The improvement between Wafer 1 and Wafer 2 is small because the longer POA causes addition thermal oxidation [32]. The low mobility of p-MOSFET is due to the combination of heavier effective mass of hole than electron for SiC [33] and lack of passivation of traps near valence band which will be explained later. Also, due to low field-effectmobility and use of only n-type polysilicon as the gate, the threshold voltage is higher for the p-MOSFET compared to n-MOSFET and will need further optimization for CMOS applications.

Figure 2. Room temperature transfer characteristics of (a) n-MOSFET and (b) p-MOSFET. The electrical oxide thickness is different from what shown in the figure since the POA/PDA have further oxidation that results in a different  $C_{OX}$ .

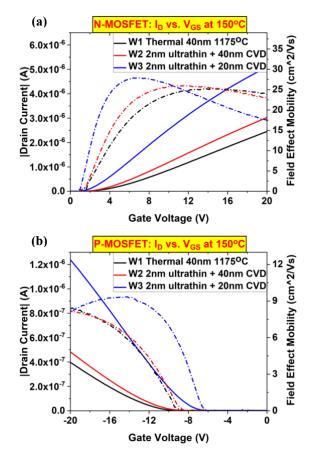

The transfer characteristics at elevated temperature (150°C) are shown in Fig. 3. The mobility increases to 25~27 cm²/Vs for n-MOSFET and 8~9 cm²/Vs for p-MOSFET. The threshold voltage decreases in magnitude for both n- and p-channel MOSFETs at elevated temperatures due to more available carriers in the channel at that temperature. The increase in mobility and decrease in threshold voltage for both n- and p-MOSFET indicates that the mobility is coulombic scattering limited. It is also observed that the thinner dielectric (Wafer 3) has smaller threshold voltage since threshold voltage is directly proportional to the dielectric thickness [31].

Figure 3. Transfer characteristics of (a) n-MOSFET and (b) p-MOSFET at 150°C. At elevated temperature, there is more carrier available for conduction and the current increases. Both n-and p-MOSFET mobility increases with temperature indicating coulombic scattering limited mobility.

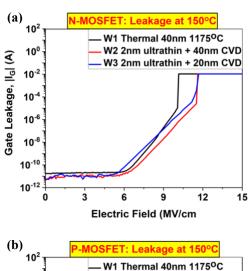

Fig. 4 shows the gate leakage characteristics measured at 150°C for n- and p-MOSFETs. For this measurement, source, drain, and substrate terminals were tied together and kept at zero bias while a voltage was applied to the gate. Voltages applied to the gate were translated to corresponding electric field using the definition from Section III. The breakdown field of n-MOSFETs occurs 10.2 MV/cm for thermal oxide (W1) and 11.6 MV/cm for ultrathin thermal + CVD oxides (W2 and W3). The p-MOSFETs have slightly lower breakdown field, likely due to traps near the valance band. Ultrathin + CVD oxides have higher breakdown fields than thermal oxide due to higher C-related traps and defects during thermal oxidation [34]. It is important to note that the p-MOSFET leakage currents start to increase at approximately -2 MV/cm for thermal oxide and at -3 MV/cm (Wafer 2) and 2.8 MV/cm (Wafer 3) for ultrathin + CVD oxides while the n-MOSFET leakage currents start increasing above 5 MV/cm.

Figure 4. Gate oxide leakage currents vs applied electric field for (a) n-MOSFET and (b) p-MOSFET. Ultrathin + CVD oxides have higher breakdown field than thermal oxides.

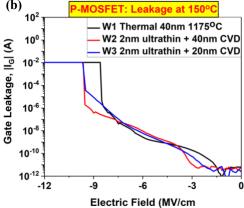

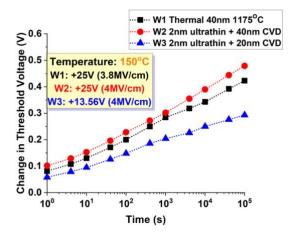

Positive bias temperature instabilities (PBTI) of n-MOSFETs on three Wafers are illustrated in Fig. 5. All three Wafers show similar behavior under +4 MV/cm stress. The shift in threshold voltage was linear in log(time) scale and less than 0.5 V after 100,000 seconds at 150°C. It is noted that the applied voltage was set to +13.56 V to achieve an effective oxide electric field of +4 MV/cm for wafer 3 as it has thinner oxide thickness compared to Wafer 1 and Wafer 2. The linear change in threshold voltage with time in log scale is attributed to the charging of as-processed oxide traps located at/near interface states. Since the shift in V<sub>TH</sub> did not lead to additional permanent trap creation [35] the stressed devices recovered to the initial value within two days from the removal of the stress. The leakage current is below 10<sup>-10</sup> A at +4 MV/cm in the time-zero leakage current plot shown in Fig. 4(a) for all three wafers.

Figure 5. PBTI on n-MOSFETs with +4 MV/cm stress at 150°C. Wafer 3 has the least shift in threshold voltage (+0.29V) and Wafer 2 has the most (+0.48 V). As Wafer 1 has thicker EOT, +25 V gives slightly lower effective electric field and has lower shift (+0.423 V) compared to Wafer 2.

Fig. 6 shows the PBTI on n-MOSFET at +25V stress. As Wafer 3 has a thinner EOT, this voltage results in +7.8 MV/cm of an effective electric field across the dielectric. From Fig. 4(a), +7.8 MV/cm falls within the Fowler-Nordheim (FN) tunneling region [36]. Due to the large injection of charges into the dielectric via FN tunneling when stressed, a second slope was observed after  $4\times10^3$  seconds. We define the slope in PBTI characteristics as  $d(\partial V_{TH})/d(log_{10}t)$ . The first and the second slopes are defined before and after  $4\times10^3$  seconds respectively. The  $2^{nd}$  slope is 1.44 while the  $1^{st}$  slope is 0.11 for Wafer 3 at +25V stress. PBTI on the thinner EOT n-MOSFET with two slopes did not recover even after two months whereas others recovered within two days. This suggests generation of traps during stress applied in BTI measurements.

Figure 6. PBTI on n-MOSFETs with +25 stress at 150°C. Wafer 3 has thinner EOT resulting 7.8MV/cm effective electric field and operating in FN tunneling region. The MOSFET on Wafer 3 did not recover after two months of relaxation.

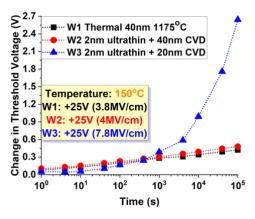

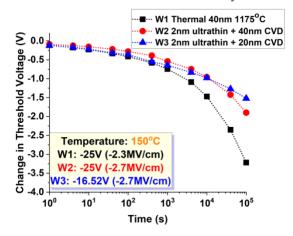

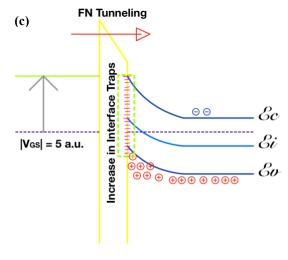

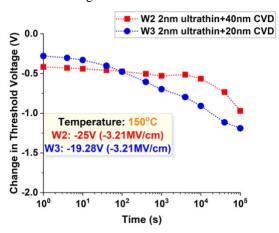

Negative bias temperature instabilities (NBTI) on p-MOSFETs are reported in Fig. 7. The p-MOSFETs on different Wafers were stressed at -25V for Wafer 1 and Wafer 2, and at -

16.52V for Wafer 3. The shift in threshold voltage is much higher for NBTI as the devices were stressed near high injection region (Fig. 4(b)). Larger shift (-3.219V) was observed for Wafer 1 at -2.3 MV/cm (-25V) compared to Wafer 2 (-1.9V at -2.7 MV/cm) and Wafer 3 (-1.52V at -2.7 MV/cm). All three curves show two slopes, and they did not recover after two days as it did for n-MOSFETs. The two slopes originate from high injection and the high injection comes from a combination of FN tunneling and trap-assisted tunneling (TAT). Thermal oxide shows the worst NBTI characteristics because the device is already operating at high injection region as it appears in the leakage current characteristics (Fig. 4). Even though the negative BTI on p-MOSFETs of Wafer 2 and 3 operates below the FN tunneling dominant region, they have 2<sup>nd</sup> slope. To investigate this, we vary the electric field stress. As the ultrathin + CVD oxides perform better than thermal oxides, we focus on further BTI measurements on Wafer 2 and 3 only.

Figure 7. NBTI on p-MOSFETs with -2.3 and -2.7MV/cm stress at 150°C. p-MOSFETs on all three Wafers show two slopes and they do not recover. Thermal oxide has higher slope and higher shift in threshold voltage compared to ultrathin + CVD oxides.

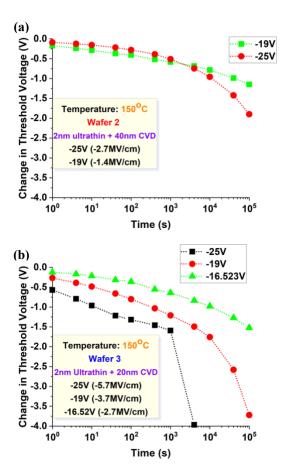

Fig. 8 shows NBTI on p-MOSFETs of Wafer 2 and Wafer 3 at different electric field stresses. As the stress was reduced in magnitude from -2.7MV/cm to -1.4MV/cm, the secondary slope reduced from -0.82 to -0.33. As we move further away from high injection region, there is still a second slope. It is evident that while the interface passivation technique used with N<sub>2</sub>O was able to passivate the traps near the conduction band, it was not able to fully passivate the traps near the valence band. Hence, the stress applied for 100,000 seconds not only keep filling the existing traps but also create new traps by injecting charges through TAT and the secondary slope persists. During relaxation, there is -0.11V shift in threshold voltage after three days for -1.4MV/cm while the device stressed at -2.7MV/cm had -1V shift in threshold voltage after two months. Wafer 3 was stressed with -16.523, -19 and -25V, for 100,000 seconds as shown in Fig. 8(b). As the bias was increasing, the 1<sup>st</sup> slope was also increasing as the devices were pushed further into FN injection region. The 1st slopes are -0.176, -0.316 and -0.35 while the 2<sup>nd</sup> slopes are -0.49, -1.5 and -3.94 for -16.523, -19 and -25V respectively. Device stressed with -16.523 recovered completely after seven days, device stressed with -19 had -0.178V shift after three weeks and the device stressed with -25V failed during measurement.

Figure 8. (a) NBTI of p-MOSFETs on Wafer 2 at 150°C. The devices were stressed with -2.7 and -1.4MV/cm. The 2<sup>nd</sup> slope reduced from -0.82 to -0.33. (b) NBTI of p-MOSFETs on Wafer 3 at 150°C. The devices were stressed at -2.7, -3.7 and -5.7MV/cm for 100,000 seconds. At -5.7 MV/cm, the device destructively broke at some point between 4000 and 10,000 seconds.

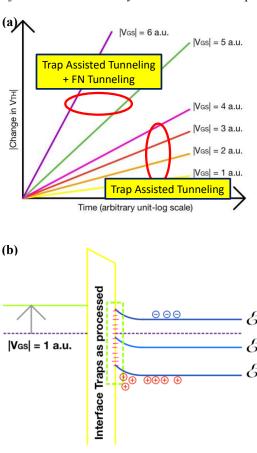

From the results, it is clear that all NBTI measurements (both n-MOSFETs and p-MOSFETs) have two slopes. The second slope can be lowered if the applied electric field stress is reduced but it is still present. Even at reduced stress there is a second slope. A hypothesis is presented in Fig. 9 to realize the reason for the two slopes. The constant bias stress (V<sub>GS</sub>) is varied from 1 to 6 arbitrary units (a.u.). At lower bias, the charge injection is lower and hence the slope is small. As V<sub>GS</sub> is increased, the slope of the threshold voltage change vs log(time) also increases. At  $V_{GS} = 5$  a.u. there is generation of traps as the stress field is increased and FN tunneling starts. The new rate of injection is a combination of TAT and FN tunneling and this gives a further increase in the slope. As FN tunneling process creates more traps, the BTI stress becomes harder to recover. In addition, at an elevated temperature (150°C) there are more carriers available for capture and the trapping/detrapping barrier is lowered [37]. As the negative bias stress is applied, the positive charges pile up near the SiO<sub>2</sub>/SiC interface which results in a negative shift in threshold voltage. Hole capture continues with time and hence the threshold voltage keeps increasing. As the applied voltage is further increased in magnitude, there is a generation of traps as well as more positive charges at a higher voltage. The second slope is from a

two-fold effect with the combination of trap-assisted injection and further creation of traps via FN injection [38], [39]. The 2<sup>nd</sup> slope exists at lower electric field stress because the charges from TAT can build up an internal electric field resulting in more injection. This eventually leads to a second slope.

Figure 9. (a) the voltage stress is increasing by 1 arbitrary unit in magnitude. As the stress is applied, the change in threshold voltage increase linearly with time in log scale continuous injection through trap assisted tunneling. When the applied voltage stress increases to 5 a.u. the change in threshold voltage gets a higher slope as the trap assisted tunneling is reinforced with FN tunneling and creation of new traps. (b) The band diagram of n-type MOS structure as in p-

MOSFET. (c) Change in band diagram and increase in the number of traps with increasing negative bias for p-type semiconductor MOS capacitor.

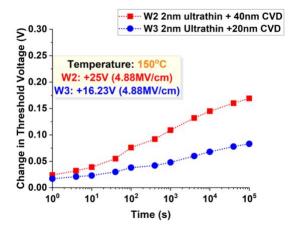

Fig. 10 shows the NBTI on n-MOSFET and PBTI on p-MOSFET for the completion of CMOS reliability. The PBTI on p-MOSFET shows excellent stability; +0.169V and +0.083 shift in threshold voltage for Wafer 2 and Wafer 3 respectively after 100,000 seconds of 4.88MV/cm stress at 150°C. On the other hand, NBTI on n-MOSFET shows -0.97V and -1.189V shift in threshold voltage for Wafer 2 and Wafer 3 respectively after 100,000 seconds of -3.21MV/cm stress at 150°C. It is clearly observed that the NBTI has a high shift in threshold voltage compared to the PBTI regardless of n-channel or pchannel MOSFET. As a result, we conclude that the high shift is due to the lack of interface passivation near the valance band of the SiC substrate. At negative bias, holes are accumulated near the valence band while at positive bias, electrons are accumulated near the conduction band. N2O and N2 annealing performed during POA/PDA steps only passivate the traps near conduction band and the valence band passivation is incomplete. Thus, NBTI on both n- and p-MOSFET shows high shift in threshold voltage due to a high probability of interface traps assisted tunneling.

Figure 10. (a) NBTI on n-MOSFET. The large shift in threshold voltage (-0.97V for Wafer 2 and -1.189V for Wafer 3) is due to lack of traps passivation such as oxygen vacancy. (b) PBTI on p-MOSFET.

The curve shows excellent passivation of interface states near conduction band for p-MOSFET.

#### V. Conclusion

This work illustrates the BTI characteristics for potential high-temperature SiC CMOS applications. Excellent PBTI on n- and p-channel MOSFETs for both thermal and ultrathin + CVD oxides has been demonstrated. PBTI on p-MOSFETs with deposited oxides are better even at higher electric field stress compared to n-MOSFETs due to less available carrier at the n-type substrate during positive applied stress. However, the NBTI characteristics suggest that the passivation of traps near the valence band is insufficient and separate post-oxidation annealing is needed. There is a significant decrease in traps near valence band of the pMOSFETs with ultrathin + CVD oxides as compared to thermal oxides as the NBTI shifts are lower for the deposited oxides.

### REFERENCE:

- W. J. Choyke and G. Pensl, "Physical Properties of SiC," MRS Bull., vol. 22, no. 3, pp. 25–29, Mar. 1997, doi: 10.1557/S0883769400032723.

- [2] Z. Chen, Y. Yao, D. Boroyevich, K. D. T. Ngo, P. Mattavelli, and K. Rajashekara, "A 1200-V, 60-A SiC MOSFET Multichip Phase-Leg Module for High-Temperature, High-Frequency Applications," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2307–2320, May 2014, doi: 10.1109/TPEL.2013.2283245.

- [3] T.-K. Nguyen *et al.*, "Highly sensitive 4H-SiC pressure sensor at cryogenic and elevated temperatures," *Mater. Des.*, vol. 156, pp. 441–445, Oct. 2018, doi: 10.1016/j.matdes.2018.07.014.

- [4] T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications. John Wiley & Sons, 2014.

- [5] D. T. Clark et al., "High Temperature Silicon Carbide CMOS Integrated Circuits," Mater. Sci. Forum, vol. 679–680, pp. 726–729, 2011, doi: 10.4028/www.scientific.net/MSF.679-680.726.

- [6] M. Alexandru et al., "SiC Integrated Circuit Control Electronics for High-Temperature Operation," *IEEE Trans. Ind. Electron.*, vol. 62, no. 5, pp. 3182–3191, May 2015, doi: 10.1109/TIE.2014.2379212.

- [7] W. Wondrak, R. Held, E. Niemann, and U. Schmid, "SiC devices for advanced power and high-temperature applications," *IEEE Trans. Ind. Electron.*, vol. 48, no. 2, pp. 307–308, Apr. 2001, doi: 10.1109/41.915409.

- [8] S. B. Isukapati et al., "Monolithic Integration of Lateral HV Power MOSFET with LV CMOS for SiC Power IC Technology," in 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), May 2021, pp. 267–270. doi: 10.23919/ISPSD50666.2021.9452235.

- [9] G. Pensl et al., "Traps at the SiC/SiO2-Interface," MRS Online Proc. Libr. OPL, vol. 640, ed 2000, doi: 10.1557/PROC-640-H3.2.

- [10] E. Pippel, J. Woltersdorf, H. Ö. Ólafsson, and E. Ö. Sveinbjörnsson, "Interfaces between 4H-SiC and SiO2: Microstructure, nanochemistry, and near-interface traps," *J. Appl. Phys.*, vol. 97, no. 3, p. 034302, Feb. 2005, doi: 10.1063/1.1836004.

- [11] K. Fujihira et al., "Characteristics of 4H–SiC MOS interface annealed in N2O," Solid-State Electron., vol. 49, no. 6, pp. 896–901, Jun. 2005, doi: 10.1016/j.sse.2004.10.016.

- [12] H. Li, S. Dimitrijev, H. B. Harrison, and D. Sweatman, "Interfacial characteristics of N2O and NO nitrided SiO2 grown on SiC by rapid thermal processing," *Appl. Phys. Lett.*, vol. 70, no. 15, pp. 2028–2030, Apr. 1997, doi: 10.1063/1.118773.

- [13] P. Jamet and S. Dimitrijev, "Physical properties of N2O and NO-nitrided gate oxides grown on 4H SiC," Appl. Phys. Lett., vol. 79, no. 3, pp. 323– 325, Jul. 2001, doi: 10.1063/1.1385181.

- [14] J. H. Moon et al., "Electrical Properties of the La2O3/4H-SiC Interface Prepared by Atomic Layer Deposition Using La(iPrCp)3 and H2O," Mater. Sci. Forum, vol. 527–529, pp. 1083–1086, 2006, doi: 10.4028/www.scientific.net/MSF.527-529.1083.

- [15] A. O'Neill, F. Arith, J. Urresti, K. Vasilevskiy, N. Wright, and S. Olsen, "High Mobility 4H-SiC MOSFET," in 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Oct. 2018, pp. 1–4. doi: 10.1109/ICSICT.2018.8564911.

- [16] X. Y. Yang, B. M. Lee, and V. Misra, "High Mobility 4H-SiC MOSFETs Using Lanthanum Silicate Interface Engineering and ALD Deposited SiO2," *Mater. Sci. Forum*, vol. 778–780, pp. 557–561, 2014, doi: 10.4028/www.scientific.net/MSF.778-780.557.

- [17] K. Król, N. Kwietniewski, S. Gierałtowska, Ł. Wachnicki, and M. Sochacki, "Electronic Properties of Stacked ZrO2 Films Fabricated by Atomic Layer Deposition on 4H-SiC," *Acta Phys. Pol. A*, vol. 132, no. 2, pp. 329–331, Aug. 2017, doi: 10.12693/APhysPolA.132.329.

- [18] Q. Song, Y. Zhang, Y. Zhang, X. Tang, and R. Jia, "Atomic layer deposited high-k HfxAl(1-x)O as an alternative gate dielectric for 4H-SiC MIS based transistors," Sci. China Technol. Sci., vol. 55, no. 3, pp. 606–609, Mar. 2012, doi: 10.1007/s11431-011-4697-1.

- [19] V. V. A. ev, F. Ciobanu, S. Dimitrijev, G. Pensl, and A. Stesmans, "Band alignment and defect states at SiC/oxide interfaces," *J. Phys. Condens. Matter*, vol. 16, no. 17, pp. S1839–S1856, Apr. 2004, doi: 10.1088/0953-8984/16/17/019.

- [20] A. J. Lelis, R. Green, and D. B. Habersat, "SiC MOSFET threshold-stability issues," *Mater. Sci. Semicond. Process.*, vol. 78, pp. 32–37, May 2018, doi: 10.1016/j.mssp.2017.11.028.

- [21] A. J. Lelis et al., "Time Dependence of Bias-Stress-Induced SiC MOSFET Threshold-Voltage Instability Measurements," *IEEE Trans. Electron Devices*, vol. 55, no. 8, pp. 1835–1840, Aug. 2008, doi: 10.1109/TED.2008.926672.

- [22] L. C. Yu, G. T. Dunne, K. S. Matocha, K. P. Cheung, J. S. Suehle, and K. Sheng, "Reliability Issues of SiC MOSFETs: A Technology for High-Temperature Environments," *IEEE Trans. Device Mater. Reliab.*, vol. 10, no. 4, pp. 418–426, Dec. 2010, doi: 10.1109/TDMR.2010.2077295.

- [23] T. Liu, S. Zhu, M. H. White, A. Salemi, D. Sheridan, and A. K. Agarwal, "Time-Dependent Dielectric Breakdown of Commercial 1.2 kV 4H-SiC Power MOSFETs," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 633–639, 2021, doi: 10.1109/JEDS.2021.3091898.

- [24] A. J. Lelis, D. B. Habersat, G. Lopez, J. M. McGarrity, F. B. McLean, and N. Goldsman, "Bias Stress-Induced Threshold-Voltage Instability of SiC MOSFETs," *Mater. Sci. Forum*, vol. 527–529, pp. 1317–1320, 2006, doi: 10.4028/www.scientific.net/MSF.527-529.1317.

- [25] R. Green, A. Lelis, and D. Habersat, "Threshold-voltage biastemperature instability in commercially-available SiC MOSFETs," *Jpn. J. Appl. Phys.*, vol. 55, no. 4S, p. 04EA03, Mar. 2016, doi: 10.7567/JJAP.55.04EA03.

- [26] C. Yang, S. Wei, and D. Wang, "Bias temperature instability in SiC metal oxide semiconductor devices," *J. Phys. Appl. Phys.*, vol. 54, no. 12, p. 123002, Jan. 2021, doi: 10.1088/1361-6463/abcd5e.

- [27] K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin, and H. Reisinger, "Review on SiC MOSFETs High-Voltage Device Reliability Focusing on Threshold Voltage Instability," *IEEE Trans. Electron Devices*, vol. 66, no. 11, pp. 4604–4616, Nov. 2019, doi: 10.1109/TED.2019.2938262.

- [28] J. R. Hauser and K. Ahmed, "Characterization of ultra-thin oxides using electrical C-V and I-V measurements," AIP Conf. Proc., vol. 449, no. 1, pp. 235–239, Nov. 1998, doi: 10.1063/1.56801.

- [29] L. Dobrescu, M. Petrov, D. Dobrescu, and C. Ravariu, "Threshold voltage extraction methods for MOS transistors," in 2000 International Semiconductor Conference. 23rd Edition. CAS 2000 Proceedings (Cat. No.00TH8486), Oct. 2000, vol. 1, pp. 371–374 vol.1. doi: 10.1109/SMICND.2000.890257.

- [30] "Mobility," in Semiconductor Material and Device Characterization, John Wiley & Sons, Ltd, 2005, pp. 465–522. doi: 10.1002/0471749095.ch8.

- [31] Y. Tsividis, Operation and modeling of the MOS transistor. USA: McGraw-Hill, Inc., 1987.

- [32] J. Rozen, S. Dhar, M. E. Zvanut, J. R. Williams, and L. C. Feldman, "Density of interface states, electron traps, and hole traps as a function of the nitrogen density in SiO2 on SiC," *J. Appl. Phys.*, vol. 105, no. 12, p. 124506, Jun. 2009, doi: 10.1063/1.3131845.

- [33] R. Kumar Chanana, "Determination of hole effective mass in SiO2 and SiC conduction band offset using Fowler–Nordheim tunneling characteristics across metal-oxide-semiconductor structures after applying oxide field corrections," *J. Appl. Phys.*, vol. 109, no. 10, p. 104508, May 2011, doi: 10.1063/1.3587185.

- [34] K. McDonald *et al.*, "Characterization and modeling of the nitrogen passivation of interface traps in SiO2/4H–SiC," *J. Appl. Phys.*, vol. 93, no. 5, pp. 2719–2722, Mar. 2003, doi: 10.1063/1.1542935.

- [35] T. Okunishi et al., "Reliability study on positive bias temperature instability in SiC MOSFETs by fast drain current measurement," Jpn. J. Appl. Phys., vol. 56, no. 4S, p. 04CR01, Jan. 2017, doi: 10.7567/JJAP.56.04CR01.

- [36] P. Fiorenza, A. Frazzetto, A. Guarnera, M. Saggio, and F. Roccaforte, "Fowler-Nordheim tunneling at SiO2/4H-SiC interfaces in metal-oxidesemiconductor field effect transistors," *Appl. Phys. Lett.*, vol. 105, no. 14, p. 142108, Oct. 2014, doi: 10.1063/1.4898009.

- [37] C. T. Yen et al., "Negative Bias Temperature Instability of SiC MOSFET," Mater. Sci. Forum, vol. 858, pp. 595–598, 2016, doi: 10.4028/www.scientific.net/MSF.858.595.

- [38] S. Mahapatra, P. B. Kumar, and M. A. Alam, "Investigation and modeling of interface and bulk trap generation during negative bias temperature instability of p-MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, no. 9, pp. 1371–1379, Sep. 2004, doi: 10.1109/TED.2004.833592.

- [39] V. Huard, "Two independent components modeling for Negative Bias Temperature Instability," in 2010 IEEE International Reliability Physics Symposium, May 2010, pp. 33–42. doi: 10.1109/IRPS.2010.5488857.